30-OCT-1999

This is the General Instruments AY-3-8910 / 8912 Programmable Sound Generator (PSG) data Manual.

This was scanned and converted using adobe capture and adobe acrobat to convert it into a .pdf.

Keep in mind that the OCR function is not perfect and you should be careful of typos and other errors introduced by the conversion process.

# AY-3-8910/8912 PROGRAMMABLE SOUND GENERATOR DATA MANUAL

- Note: Registers are in Octal. Chart shown on page 11 shows Channel A amplitude as "RIO". In reality it is addressed as an "8". "RI1" is really "9"; "R12" is really "A" etc.

- It has been found that the PSG works well in SIOO Buss Applications using the system clock which by definition is 2MHZ. "The 2MHZ should be divided by 2 to yield 1 MHZ to allow for lower noise frequencies. This eliminates the need for an external clock as shown on page 33.

**Note:** Pages 3-4; 30, 31, 60-64 have been excluded. The booklet does include all information available at this time.

Portions of this book have been reprinted with permission from the original General Instrument **Ay-3-8910/8912 DATA MANUAL.** Neither General Instruments nor this company assume responsibility for the accuracy or use of any of the information described herein.

## **1 INTRODUCTION**

It is apparent that any microprocessor is capable of producing acceptable sounds with only a transducer if the processor has no other tasks to perform while the sound is sustained. In real world microprocessor use, however, video games need refreshing, keyboards need scanning, etc. For example, in order to produce a single channel of ninth octave C (8372 Hz) the signal needs attention every sixty microseconds. Software required to produce this simple effect and still perform other activities would in the least be very complex if not impossible. In the extreme, random noise requires periodic attention even more frequently.

This need for software-produced sounds without the constant attention of the processor is now satisfied with the availability of the General Instrument AY-3-8910 and AY-3-8912 Programmable Sound Generators.

1.1 Description

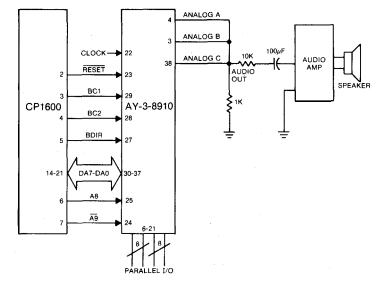

The AY-3-8910/8912 Programmable Sound Generator (PSG) is a Large Scale Integrated Circuit which can produce a wide variety of complex sounds under software control. The AY-3-8910/8912 is manufactured in GI's N-Channel Ion Implant Process. Operation requires a single 5V power supply, a TTL compatible clock, and a microprocessor controller such as the GI 16-bit CP1600/1610 or one of GI's PIC 1650 series of b-bit microcomputers.

The PSG is easily interfaced to any bus oriented system. Its flexibility makes it useful in applications such as music synthesis, sound effects generation, audible alarms, tonesignalling and FSK modems. The analog sound outputs can each provide 4 bits of logarithmic digital to analog conversion, greatly enhancing the dynamic range of the sounds produced.

In order to perform sound effects while allowing the processor to continue its other tasks, the PSG can continue to produce sound after the initial commands have been given by the control processor. The fact that realistic sound production often involves more than one effect is satisfied by the three independently controllable channels available in the PSG.

All of the circuit control signals are digital in nature and intended to be provided directly by a microprocessor/microcomputer. This means that one PSG can produce the full range of required sounds with no change in external circuitry. Since the frequency responseof the PSG ranges from sub-audible at its lowest frequency to postaudible at its highest frequency, there are few sounds which are beyond reproduction with only the simplest electrical connections.

Since most applications of a microprocessor/PSG system would also require interfacing between the outside world and the microprocessor, this facility has been designed into the PSG. The AY-3-8910 has two general purpose 8-bit I/O ports and is supplied in a 40 lead package; the AY-3-8912 has one port and 28 leads.

- 1.2 > Full software control of sound generation.

- > Interfaces to most 8-bit and 16-bit microprocessors.

- Features D Three independently programmed analog outputs.

- > Two 8-bit general purpose I/O ports (AY-3-8910).

- > One 8-bit general purpose I/O port (ÀY-3-8912).

- > Single +5 Volt Supply.

- Scope

1 3 This Data Manual is intended to introduce the techniques needed to cause the AY-3-8910/8912 Programmable Sound Generator to perform in its intended fashion. All of the programs, programming, and hardware designs have been tested to ensure that the methods are practical rather than purely theoretical.

Although the techniquesdescribed will produce powerful results, the range of sounds to be synthesized is so vast and the PSG capabilities so varied that this guide should be viewed merely as an introduction to the applications possibilities of the PSG.

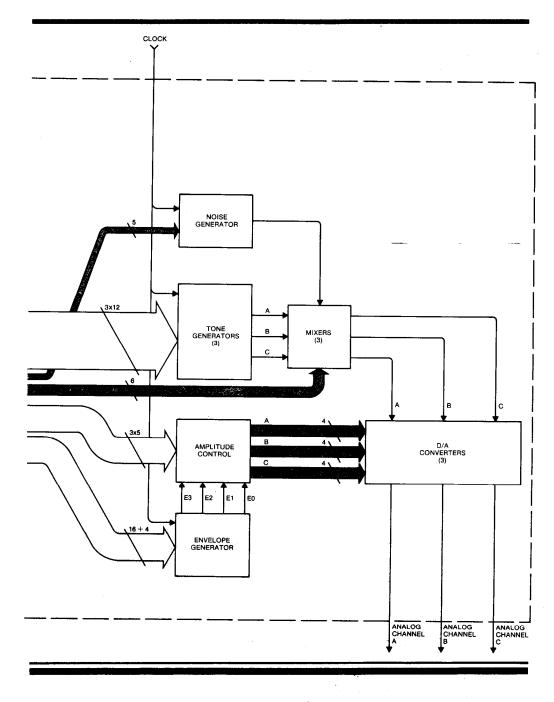

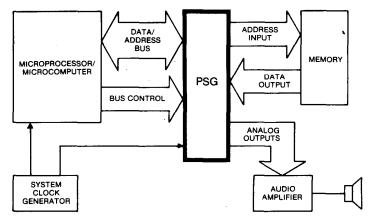

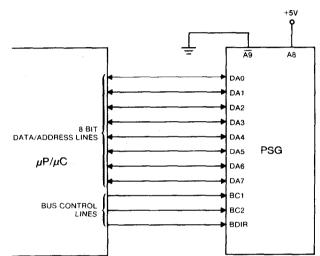

Fig. 1 TYPICAL SYSTEM DIAGRAM

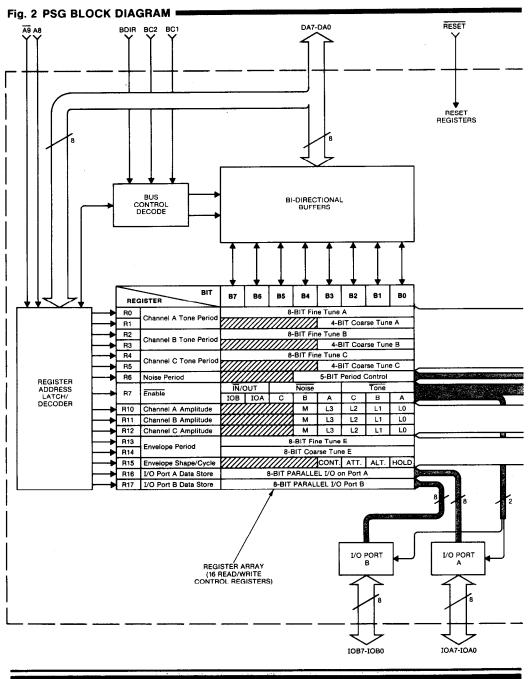

## **2 ARCHITECTURE**

The AY-3-8910/8912 is a register oriented Programmable Sound Generator (PSG). Communication between the processor and the PSG is based on the concept of memory-mapped I/O. Control commands are issued to the PSG by writing to 16 memory-mapped registers. Each of the 16 registers within the PSG is also readable so that the microprocessor can determine, as necessary, present states or stored data values.

All functions of the PSG are controlled through its 16 registers which once programmed, generate and sustain thesounds, thus freeing the system processor for other tasks.

2.1 An internal block diagram of the PSG showing the various functional blocks and data flow is shown in Fig. 2.

## Basic Functional Blocks

### 2.1.1 REGISTER ARRAY

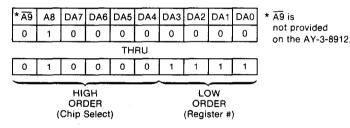

The principal element of the PSG is the array of 16 read/write control registers. These 16 registers look to the CPU as a block of memory and as such occupy a 16 word block out of 1,024 possible addresses. The 10 address bits (8 bits on the common data/address bus, and 2 separate address bits A8 and \*A9) are decoded as follows:

The four low order address bits select one of the 16 registers (R0--R17<sub>8</sub>). The six high order address bits function as "chip selects" to control the tri-state bidirectional buffers (when the high order address bits are "incorrect", the bidirectional buffers are forced to a high impedance state). High order address bits A9 A8 are fixed in the PSG design to recognize a 01 code; high order address bits DA7--DA4 may be mask-programmed to any 4-bit code by a special order factory mask modification. Unless otherwise specified, address bits DA7--DA4 are programmed to recognize only a 0000 code. A valid high order address latches the register address (the low order 4 bits) in the Register Address Latch/Decoder block. A latched address will remain valid until the receipt of a new address, enabling multiple reads and writes of the same register contents without the need for redundant re-addressing.

## 21 Basic Functional Blocks (cont.)

Conditioning of the Register Address Latch/Decoder and the Bidirectional Buffers to recognize the bus function required (inactive, latch address, write data, or read data) is accomplished by the Bus Control Decode block.

The function of each of the 16 PSG registers and the data flow of each register's contents are shown in context in Fig. 2 and explained in detail in Section 3, "Operation". For reference purposes, the Register Array details are reproduced in Fig. 3.

## 2.1.2 SOUND GENERATING BLOCKS

| The basic | blocks | in | the | PSG | which | produce | the | programmed | sounds |

|-----------|--------|----|-----|-----|-------|---------|-----|------------|--------|

| include:  |        |    |     |     |       | •       |     |            |        |

| Tone Generators    | produce the basic square wave tone frequen-<br>cies for each channel (A,B,C)                                                                                                                                           |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Noise Generator    | produces a frequency modulated pseudo<br>random pulse width square wave output.                                                                                                                                        |

| Mixers             | combine the outputs of the Tone Generators<br>and the Noise Generator. One for each chan-<br>nel (A,B,C).                                                                                                              |

| Amplitude Control  | provides the D/A Converters with either a fixed or variable amplitude pattern. The fixed amplitude is under direct 'CPU control; the variable amplitude is accomplished by using the output of the Envelope Generator. |

| Envelope Generator | produces an envelope pattern which can be<br>used to amplitude modulate the output of<br>each Mixer.                                                                                                                   |

| D/A Converters     | the three D/A Converters each produce up to<br>a 16 level output signal as determined by the<br>Amplitude Control.                                                                                                     |

#### 2.1.3 I/O PORTS

Two additional blocks are shown in the PSG Block Diagram which have nothing directly to do with the production of sound-these are the two I/O Ports (A and B). Since virtually all uses of microprocessor-based sound. would require interfacing between the outside world and the processor, this facility has been included in the PSG. Data to/from the CPU bus may be read/written to either of two 8-bit I/O Ports without affecting any other function of the PSG. The I/O Ports are TTL-compatible and are provided with internal pull-ups on each pin. Both Ports are available on the AY-3-8910; only I/O Port A is available on the AY-3-8912.

| REGIS | BIT                      | <b>B</b> 7          | B6    | <b>B</b> 5 | <b>B</b> 4 | <b>B</b> 3          | <b>B</b> 2 | 81       | BO  |  |

|-------|--------------------------|---------------------|-------|------------|------------|---------------------|------------|----------|-----|--|

| R0    | Observal & Trans Desired | 8-BIT Fine Tune A   |       |            |            |                     |            |          |     |  |

| R1    | Channel A Tone Period    | 7777                | 7777  | 7777       | ////       | 4-                  | BIT Coa    | irse Tun | e A |  |

| R2    |                          |                     |       |            | B-BIT Fir  | ne Tune             | в          |          |     |  |

| R3    | Channel B Tone Period    | ////                | ///// | /////      | /////      | 4-                  | BIT Coa    | rse Tun  | eВ  |  |

| R4    | Channel C Tone Period    | 8-BIT Fine Tune C   |       |            |            |                     |            |          |     |  |

| R5    | Channel C Tone Period    |                     |       |            |            | 4-BIT Coarse Tune C |            |          |     |  |

| R6    | Noise Period             | ////                | ////  | ////       |            | 5-                  | BIT Per    | iod Cont | rol |  |

| B7    | Enable                   | ĨÑ/                 | OUT   |            | Noise      |                     | Tone       |          |     |  |

| n/    | Enable                   | IOB                 | IOA   | С          | В          | A                   | С          | В        | A   |  |

| R10   | Channel A Amplitude      |                     |       |            | м          | L3                  | L2         | L1       | L0  |  |

| R11   | Channel B Amplitude      |                     |       |            | м          | L3                  | L2         | L1       | LO  |  |

| R12   | Channel C Amplitude      | ////                |       | ////       | м          | L3                  | L2         | L1       | LO  |  |

| R13   | Envelope Beried          | 8-BIT Fine Tune E   |       |            |            |                     |            |          |     |  |

| R14   | Envelope Period          | 8-BIT Coarse Tune E |       |            |            |                     |            |          |     |  |

| R15   | Envelope Shape/Cycle     |                     |       |            |            | CONT.               | ATT.       | ALT.     | HOL |  |

| R16   | I/O Port A Data Store    |                     |       | 8-BIT F    | PARALLI    | EL I/O o            | n Port A   |          |     |  |

| R17   | I/O Port B Data Store    |                     |       | 8-BIT      | PARAL      | LEL I/O             | Port B     |          |     |  |

## Fig. 3 PSG REGISTER ARRAY

2.2 The AY-3-8910 is supplied in a 40 lead dual in-line package with the pm assignments as shown in Fig. 4. The AY-3-8912 is supplied in a28 lead dual in-line package with the pin assignments as shown in Fig. 5.

## Fig. 4 AY-3-8910 PIN ASSIGNMENTS

|                         | Top Vi      | iew  |                       |

|-------------------------|-------------|------|-----------------------|

| V <sub>ss</sub> (GND) [ | <b>•</b> 1  | 40   | V <sub>cc</sub> (+5V) |

| N.C. [                  | 2           | 39 🗖 | TEST 1                |

| ANALOG CHANNEL B        | 3           | 38 🗖 | ANALOG CHANNE         |

| ANALOG CHANNEL A        | 4           | 37 🗖 | DA0                   |

| N.C. [                  | 5           | 36 🗖 | DA1                   |

| IOB7 [                  | 6           | 35 🗖 | DA2                   |

| IOB6 [                  | 7           | 34 🗖 | DA3                   |

| IOB5 [                  | 8           | 33 🗖 | DA4                   |

| IOB4 [                  | 9           | 32 🗖 | DA5                   |

| IOB3 [                  | 10          | 31   | DA6                   |

| IOB2 [                  | <b>1</b> 11 | 30 🗖 | DA7                   |

| IOB1                    | 12          | 29 🗖 | BC1                   |

| IOB0 [                  | 13          | 28 🗖 | BC2                   |

| IOA7 [                  | 14          | 27   | BDIR                  |

| IOA6 [                  | 15          | 26 🗖 | TEST 2                |

| IOA5 [                  | 16          | 25 🗖 | A8                    |

| IOA4 [                  | 17          | 24 🗖 | A9                    |

| IOA3 (                  | 18          | 23 🗖 | RESET                 |

| IOA2 [                  | 19          | 22   | CLOCK                 |

| IOA1 [                  | 20          | 21   | IOA0                  |

|                         | •           |      |                       |

## Fig. 5 AY-3-8912 PIN ASSIGNMENTS

|                           | Top View |       |

|---------------------------|----------|-------|

| ANALOG CHANNEL C          | 28       | DA0   |

| TEST 1 🗖 2                | 27 🗖     | DA1   |

| V <sub>cc</sub> (+5V) 🗖 3 | 26       | DA2   |

| ANALOG CHANNEL B          | 25       | DA3   |

| ANALOG CHANNEL A          | 24       | DA4   |

| V <sub>ss</sub> (GND) 🗖 6 | 23       | DA5   |

|                           | 22       | DA6   |

| IOA6 🗆 8                  | 21       | DA7   |

|                           | 20       | BC1   |

| IOA4 🗖 10                 | 19       | BC2   |

| IOA3 🗖 11                 | 18       | BDIR  |

| IOA2 🗖 12                 | 17       | A8    |

| IOA1 🗖 13                 | 16       | RESET |

|                           | 15       | CLOCK |

kage with the upplied in a 28 hown in Fig. 5.

#### Pin Data/Address Functions 7-0:

These 8 lines comprise the 8-bit bidirectional bus used by the microprocessor to send both data and addresses to the PSG and to receive data from the PSG. In the data mode, DA7--DA0 correspond to Register Array bits B7--B0. In the address mode, DA3-DA0 select the register # (O--17) and DA7--DA4 in conjunction with address inputs A9 and A8 form the high order address (chip select).

A8 (input): pin 25 (AY-3-8910)

pin 17 (AY-3-8912)

\*A9 (input): pin 24 (AY-3-8910) (not provided on AY-3-8912)

#### \*Address 9, Address 8

These "extra" address bits are made available to enable the positioning of the PSG (assigning a 16 word memory space) in a total 1,024 word memory area rather than in a 256 word memory area as defined by address bits DA7--DA0 alone. If the memory size does not require the use of these extra address lines they may be leftunconnected as each is provided with either an on-chip pull down (A9) or pull-up (A8) resistor. In "noisy" environments, however, it is recommended that A9 and A8 be tied to an external ground and +5V, respectively, if they are not to be used.

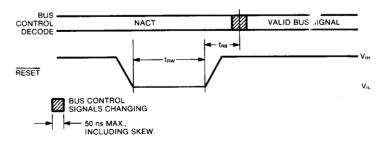

**RESET** (input): pin 23 (AY-3-8910) pin 16 (AY-3-8912)

For initialization/power-on purposes, applying logic "0" (ground) to the Reset pin will reset all registers to "0". The Reset pin is provided with an on-chip pull-up resistor.

CLOCK (input): pin 22 (AY-3-8910) pin 15 (AY-3-8912)

This TTL-compatible input supplies the timing reference for the Tone, Noise and Envelope Generators.

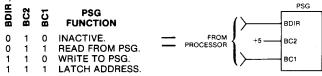

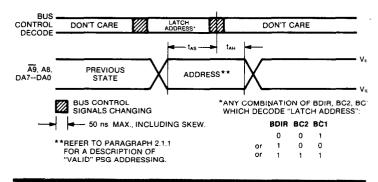

BDIR, BC2, BCI (inputs): pins 27,28,29 (AY-3-8910) pins 18,19,20 (AY-3-8912)

#### Bus DIRection, Bus Control 2,I

These bus control signals are generated directly by GI's CP1600 series of microprocessors to control all external and internal bus operations in the PSG. When using a processor other than the CP1600, these signals can be provided either by comparable bus signalsor by simulating the signals on I/O lines of the processor. The PSG decodes these signals as illustrated in the-following:

IANNEL C

## 2.3 Pin Functions (cont.)

| BOIR | BC2 | BC1 | CP1600<br>FUNCTION | PSG<br>FUNCTION                                                                                                                                                      |

|------|-----|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0   | 0   | NACT               | INACTIVE. See 010 (IAB) below.                                                                                                                                       |

| 0    | 0   | 1   | ADAR               | LATCH ADDRESS. See 111 (INTAK) below.                                                                                                                                |

| 0    | 1   | 0   | IAB                | INACTIVE. The PSG/CPU bus is inactive. DA7DA0 are in a high impedance state.                                                                                         |

| 0    | 1   | 1   | DTB                | READ FROM PSG. This signal causes the contents<br>of the register which is currently addressed to<br>appear on the PSG/CPU bus. DA7DA0 are in the<br>output mode.    |

| 1    | 0   | 0   | BAR                | LATCH ADDRESS. See 111 (INTAK) below.                                                                                                                                |

| 1    | 0   | 1   | DW                 | INACTIVE. See 010 (IAB) above.                                                                                                                                       |

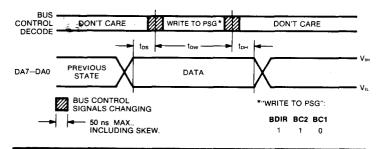

| 1    | 1   | 0   | DWS                | WRITE TO PSG. This signal indicates that the bus contains register data which should be latched into the currently addressed register. DA7DA0 are in the input mode. |

| 1    | 1   | 1   | ΙΝΤΑΚ              | LATCH ADDRESS. This signal indicates that the bus contains a register address which should be latched in the PSG. DA7DA0 are in the input mode.                      |

While interfacing to a processor other than the CP1600 would simply require simulating the above decoding, the redundancies in the PSG functions vs. bus control signals can be used to advantage in that only four of the eight possibledecoded bus functions are required by the PSG. This could simplify the programming of the bus control signals to the following, which would only require that the processor generate two bus control signals (BDIR and BCI, with BC2 tied to +5v):

### ANALOG CHANNEL A, B, C (outputs): pins 4, 3, 38 (AY-3-8910) pins 5, 4, 1 (AY-3-8912)

Each of these signals is the output of its corresponding D/A Converter, and provides an up to 1V peak-peak signal representing the complex sound waveshape generated by the PSG.

IOA7--IOAO (input/output): pins 14--21 (AY-3-8910) pins 7--14 (AY-3-8912)

IOB7--1OB0 (input/output): pins 6--13 (AY-3-8910) (not provided on AY-3-8912)

#### Input/Output A7-- AO, B7-- B0

Each of these two parallel input/output ports provides 8 bits of parallel data to/from the PSG/CPU bus from/to any external devices connected to the IOA or IOB pins. Each pin is provided with an onchip pull-up resistor, so that when in the "input" mode, all pins will read normally high. Therefore, the recommended method for scanning external switches, for example, would be to ground the input bit. **TEST 1:** pin 39 (AY-3-8910) pin 2 (AY-3-8912)

- **TEST** 2: pin 26 (AY-3-8910)

- (not connected on AY-3-8912)

These pins are for GI test purposes only and should be left open-& not use as tie-points.

Vcc: pin 40 (AY-3-8910) pin 3 (AY-3-8912)

Nominal +5Volt power supply to the PSG.

Vss: pin 1 (AY-3-8910) pin 6 (AY-3-8912)

Ground reference for the PSG.

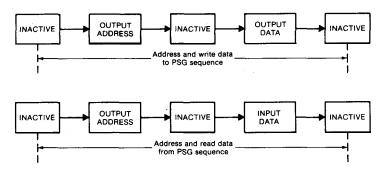

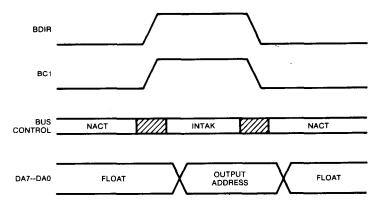

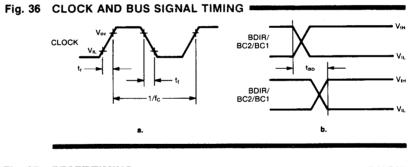

2.4 Since the PSG functions are controlled by commands from the system processor, the common data/address bus (DA7--DAO) requires definition as to its function at any particular time. This is accomplished by the processor issuing bus control signals, previously described, defining the state of the bus; the PSG then decodes these signals to perform the requested task.

The conditioning of these bus control signals by the processor is the same as if the processor were interacting with RAM: (1) the processor outputs a memory address; and (2) the processor either outputs or inputs data to/from the memory. The "memory" in this case is the PSG's array of 16 read/write control registers.

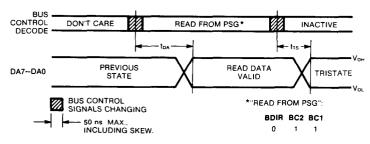

The timing relationships in issuing the bus control signals relative to the data or address signals on the bus are reviewed in general in the following section, and in detail in Section 7, Electrical Specifications. State Timing

2.5 While the state flow for many microprocessors can be somewhat involved for certain operations, the sequence of events necessary to control the PSG is simple and straightforward. Each of the three major state sequences (Latch Address, Write to PSG, and Read from PSG) consists of several operations (indicated below by rectangular blocks), defined by the pattern of bus control signals (BDIR, BC2, BCI).

The functional operation and relative timing of the PSG control sequences are described in the following paragraphs (in all examples, BC2 has been assumed to be tied to logic "1", +5V).

#### 2.5.1 ADDRESS PSG REGISTER SEQUENCE

The "Latch Address.". sequence is normally an integral part of the write or read sequences, but for simplicity is illustrated here as an individual sequence. Depending on the processor used the program sequence will normally require four principal microstates: (1) send NACT (inactive); (2) send INTAK (latch address); (3) put address on bus: (4) send NACT (inactive). [Note: within the timing constraints detailed in Section 7, steps (2) and (3) may be interchanged.]

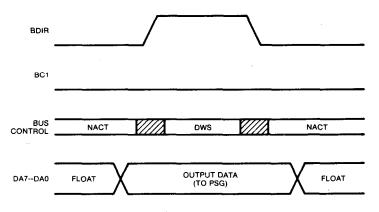

#### 2.5.2 WRITE DATA TO PSG SEQUENCE

The "Write to PSG" sequence, which would normally follow immediately after an address sequence, requires four principal microstates: (1) send NACT (inactive); (2) put data on bus; (3) send DWS (write to PSG); (4) send NACT (inactive).

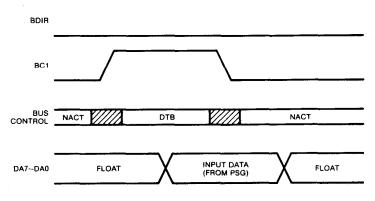

#### 2.5.3 READ DATA FROM PSG SEQUENCE

As with the "Write to PSG" sequence, the "Read from PSG" sequence would also normally follow immediately after an address sequence. The four principal microstates of the read sequence are: (1) send NACT (inactive); (2) send DTB (read from PSG); (3) read data on bus; (4) send NACT (inactive).

#### 2.5.4 WRITE TO/READ FROM I/O PORT SEQUENCE

Since the two I/O Ports (A and B) each have an 8-bit register assigned as a data store, writing to or reading from either port is identical to writing or reading to any other register. Hence, the state sequences are exactly-the same as described in the preceding paragraphs.

## **3 OPERATION**

Since all functions of the PSG are controlled by the host processor via a series of register loads, a detailed description of the PSG operation can best be accomplished by relating each PSG function to the control of its corresponding register. The function of creating or programming a specific sound or sound effect logically follows the control sequence listed:

| Section | Operation                     | Registers | Function                                                |

|---------|-------------------------------|-----------|---------------------------------------------------------|

| 3.1     | Tone Generator Control        | R0R5      | Program tone periods.                                   |

| 3.2     | Noise Generator Control       | R6        | Program noise period.                                   |

| 3.3     | Mixer Control                 | R7        | Enable tone and/or noise<br>on selected channels.       |

| 3.4     | Amplitude Control             | R10R12    | Select "fixed" or "envelope-<br>variable" amplitudes.   |

| 3.5     | Envelope Generator<br>Control | R13R15    | Program envelope period<br>and select envelope pattern. |

## Tone Generator Control

(Registers R1, R2, R3, R4, R5)

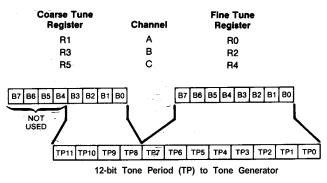

3.1 The frequency of each square wave generated by the three Tone Generators (one each for Channels A, B, and C) is obtained in the PSG by first counting down the input clock by 16, then by further counting down the result by the programmed 12-bit Tone Period value. Each 12-bit value is obtained in the PSG by combining the contents of the relative Coarse and Fine Tune registers, as illustrated in the following.

Note that the 12-bit value programmed in the combined Coarse and Fine Tune registers is a period value-the higher the value in the registers, the lower the resultant tone-frequency.

Note also that due to the design technique used in the Tone Period count-down, the lowest period value is 00000000001 (divide by 1) and the highest period value is 1111111'1111 (divide by  $4,095_{10}$ ).

The equations describing the relationship between the desired output tone frequency and the input clock frequency and Tone Period value are:

(a)

$$f_T = \frac{f_{CLOCK}}{16TP_{10}}$$

(b)  $TP_{10} = 256CT_{10} + FT_{10}$

Where: f<sub>T</sub> = desired tone frequency

fcLock = input clock frequency

- TP<sub>10</sub>=decimal equivalent of the Tone Period bits TP11--TP0.

- CT<sub>10</sub>=decimal equivalent of the Coarse Tune register bits B3--B0 (TP11--TP8)

- FT<sub>10</sub>=decimal equivalent of the Fine Tune register bits B7--B0 (TP7--TP0)

From the above equations it can be seen that the tone frequency can range from a low of  $\frac{f_{cucer}}{65,520}$  (wherein: TP<sub>10</sub>=4,095<sub>10</sub>) to a high of  $\frac{f_{cucer}}{16}$  (wherein: TP<sub>10</sub>=1). Using a 2 MHz input clock, for example, would produce a range of tone frequencies from 30.5 Hz to 125 kHz.

To calculate the values for the contents of the Tone Period Coarse and Fine Tune registers, given the input clock and the desired output tone frequencies, we simply rearrange the above equations, yielding:

(a)

$$TP_{10} = \frac{f_{CLOCK}}{16f_T}$$

(b)  $CT_{10} + \frac{FT_{10}}{256} = \frac{TP_{10}}{256}$

**Example 1:**  $f_T = 1kHz$

$$TP_{10} = \frac{2x10^{\circ}}{16(1x10^{3})} = 125$$

Substituting this result into equation (b):

$$CT_{10} + \frac{FT_{10}}{256} = \frac{125}{256}$$

$$\therefore CT_{10} = 0 = 0000 (B3-B0)$$

$$FT_{10} = 125_{10} = 01111101 (B7-B0)$$

Example 2: f<sub>T</sub> = 100Hz

$$f_{CLOCK} = 2MHz$$

TP<sub>10</sub> =  $\frac{2x10^6}{16(1x10^2)} = 1250$

Substituting this result into equation (b):

$$\begin{array}{rl} CT_{10} + \frac{FT_{10}}{256} = \frac{1250}{256} = 4 + \frac{226}{256} \\ \therefore CT_{10} = 4_{10} = 0100 \ (B3-B0) \\ FT_{10} = 226_{10} = 11100010 \ (B7-B0) \end{array}$$

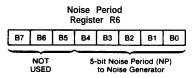

## 3.2 Noise Generator CONTROL (Register R6)

The frequency of the noise source is obtained in the PSG by first counting down the input clock by 16, then by further counting down the result by the programmed 5-bit Noise Period value. This B-bit value consists of the lower 5 bits (B4-B0) of register R6, as illustrated in the following:

Note that the 6-bit value in R11 is a period value-the higher the value in the register, the lower the resultant noise frequency. Note also that, as with the Tone Period, the lowest period value is00001 (divide by 1); the highest period value is 11111 (divide by  $31_{10}$ ).

The noise frequency equation is:

$$f_{N} = \frac{f_{CLOCK}}{16 \text{ NP}_{10}}$$

Where:  $f_{N}$  = desired noise frequency

$f_{CLOCK}$  = input clock frequency

$NP_{10}$  = decimal equivalent of the Noise Period

register bits B4--B0.

From the above equation it can be seen that the noise frequency can range from a low of  $\frac{f_{cucex}}{400}$  (wherein: NP<sub>10</sub> = 31<sub>10</sub>) to a high of  $\frac{f_{cucex}}{16}$ (wherein: NP<sub>10</sub> = 1). Using a 2 MHz input clock, for example, would produce a range of noise frequencies from 4 kHz to 125 kHz.

To calculate the value for the contents of the Noise Period register, given the input clock and the desired output noise frequencies, we simply rearrange the above equation, yielding:

$$NP_{10} = \frac{f_{CLOCK}}{16 f_N}$$

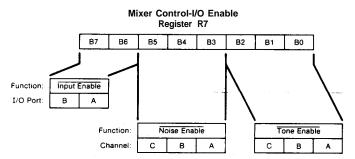

3.3 Register 7, is a multi-function Enable register which controls the three Noise/Tone Mixers and the two general purpose I/O Ports.

## Mixer Control-I/0 Enable

The Mixers, as previously described, combine the noise and tone frequencies for each of the three channels. The determination of combining neither/either/both noise and tone frequencies on each channel is made by the state of bits B5--B0 of R7.

(Register R7)

The direction (input or output ) of the two general purpose I/O Ports (IOA and IOB) is determined by the state of bits B7 and B6 of R7.

These functions are illustrated in the following:

## Noise Enable Truth Table: Tone Enable Truth Table: R7 Bits Noise Enabled R7 Bits Tone Enabled B5 B4 B3 on Channel B2 B1 B0 on Channel

|     |   |     |   | 82 | 81 | BO | on Channel |

|-----|---|-----|---|----|----|----|------------|

| 0 0 | 0 | СВ  | Α | 0  | 0  | 0  | СВА        |

| 0 0 | 1 | СВ  |   | 0  | 0  | 1  | С в —      |

| 0 1 | 0 | с — | Α | 0  | 1  | 0  | С — А      |

| 01  | 1 | с — | _ | 0  | 1  | 1  | c — —      |

| 1.0 | 0 | — В | Α | 1  | 0  | 0  | — B A      |

| 1 0 | 1 | — B |   | 1  | 0  | 1  | — B —      |

| 1 1 | 0 |     | Α | 1  | 1  | 0  | — — A      |

| 1 1 | 1 |     | _ | 1  | 1  | 1  |            |

#### I/O Port Truth Table:

| R7         | Bits | I/O Port Status |        |  |  |  |

|------------|------|-----------------|--------|--|--|--|

| <b>B</b> 7 | B6   | IOB             | 10A    |  |  |  |

| 0          | 0    | Input           | Input  |  |  |  |

| 0          | 1    | Input           | Output |  |  |  |

| 1          | 0    | Output          | Input  |  |  |  |

| 1          | 1    | Output          | Output |  |  |  |

NOTE: Disabling noise and tone does <u>not</u> turn off a channel. Turning a channel off can only be accomplished by writing all zeroes into the corresponding Amplitude Control register, R10, R11, or R12 (see Section 3.4).

## Amplitude

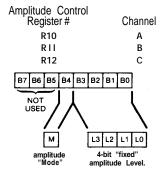

3.4 The amplitudes of the signals generated by each of the three D/A Converters (one each for Channels A, B, and C) is determined by the contents of the lower 5 bits (B4--BO) of registers R10, RI11, and R12 as illustrated in the following: control

(Registers R10, R11, R12)

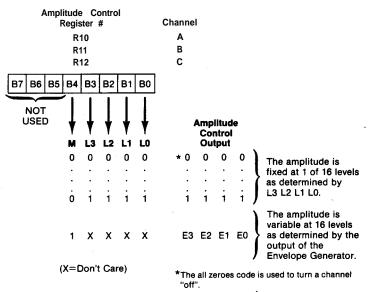

The amplitude "mode" (bit M) selects either fixed level amplitude (M=0) or variable level amplitude (M=1). It follows then that bits L3--L0, defining the value of a "fixed" level amplitude, are only active when M=0. When fixed level amplitude isselected, it is "fixed" only in the sense that the amplitude level is under the direct control of the system processor (via bits D3--D0). Varying the amplitude when in this "fixed" amplitude mode requires in each instance the direct intervention of the system processor via an address latch/write data sequence to modify the D3--D0 data.

When M=1 (select "variable" level amplitudes), the amplitude of each channel is determined by the envelope pattern as defined by the Envelope Generator's 4-bit output E3 E2 E1 EO.

The amplitude "mode" (bit M) can also be thought of as an "envelope enable" bit; i.e., when M=0 the envelope is not used, and when M=1 the envelope is enabled. (A full description of the Envelope Generator function follows in Section 3.5).

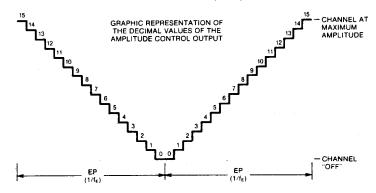

Fig. 6 graphically illustrates a selection of variable level (envelopecontrolled) amplitude where the 16 levels directly reflect the output of the Envelope Generator. A fixed level amplitude would correspond to only one of the levels shown, with the level directly determined by the decimal equivalent of bits L3 L2 L1 L0.

#### Fig. 6 VARIABLE AMPLITUDE CONTROL (M=1)

The full chart describing all combinations of the 5-bit Amplitude Control is as follows:

## Envelope Generator Control

3.5 To accomplish the generation of fairly complex envelope patterns, two independent methods of control are provided in the PSG: first, it is possible to vary the frequency of the envelope using registers R13 and R14; and second, the relative shape and cycle pattern of the envelope can be varied using register R15. The following paragraphs explain the details of the envelope control functions, describing first the envelope period control and then the envelope shape/cycle

(Registers R13, R14, R15) control.

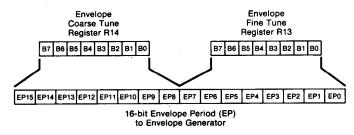

3.5.1 ENVELOPE PERIOD CONTROL (Registers R13, R14)

The frequency of the envelope is obtained in the PSG by first counting down the input clock by 256, then by further counting down the result by the programmed 16-bit Envelope Period value. This 16-bit value is obtained in the PSG by combining the contents of the Envelope Coarse and Fine Tune registers, as illustrated in the following:

Note that the 16-bit value programmed in the combined Coarse and Fine Tune registers is a period value-the higher the value in the registers, the lower the resultant envelope frequency.

Note also, that as with the Tone Period, the lowest period Value is 0000000000000001 (divide by 1); the highest period value is 11111111111111111 (divide by  $65,536_{10}$ ).

The envelope frequency equations are:

(a)  $f_E = \frac{f_{CLOCK}}{256EP_{10}}$  (b)  $EP_{10}=256CT_{10}+FT_{10}$

Where: f<sub>E</sub> = desired envelope frequency

- f<sub>CLOCK</sub>≕input clock frequency EP<sub>10</sub>=decimal equivalent of the Envelope Period bits EP15--EP0

- CT<sub>10</sub>=decimal equivalent of the Coarse Tune register bits B7--B0 (EP15--EP8)

- FT<sub>10</sub> = decimal equivalent of the Fine Tune register bits B7--B0 (EP7--EP0)

From the above equation it can bee seen that the envelope frequency can range from a low of  $\frac{f_{cocyc}}{16.776,960_{10}}$  (wherein: EP<sub>10</sub>=65,535<sub>10</sub>) to a high of  $\frac{f_{cocyc}}{256}$  (wherein: EP<sub>10</sub>=1). Using a 2 MHz clock, for example, would produce a range of envelope frequencies from 0.12 Hz to 7812.5 Hz.

To calculate the values for the contents of the Envelope Period Coarse and Fine Tune registers, given the input clock and the desired envelope frequencies, we rearrange the above equations, yielding:

(a)

$$EP_{10} = \frac{f_{CLOCK}}{2566f_E}$$

(b)  $CT_{10} + \frac{FT_{10}}{256} = \frac{EP_{10}}{256}$

**Example:**  $f_E = 0.5 \text{ Hz}$

$f_{CLOCK} = 2 \text{ MHz}$

$EP_{10} = \frac{2x10^{4}}{256(0.5)} = 15,625$

Substituting this result into equation (b):

$CT_{10} + \frac{FT_{10}}{256} = \frac{15,625}{256} = 61 + \frac{9}{256}$

$CT_{10} = 61_{10} = 00111101 (B7-B0)$

$FT_{10} = 9_{10} = 00001001 (B7-B0)$

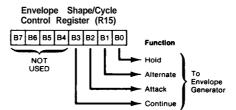

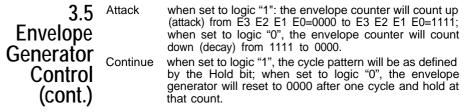

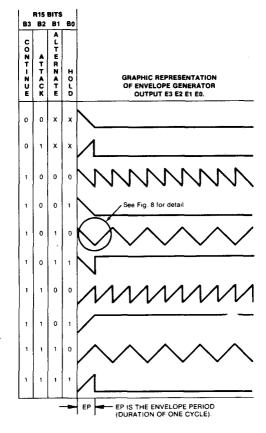

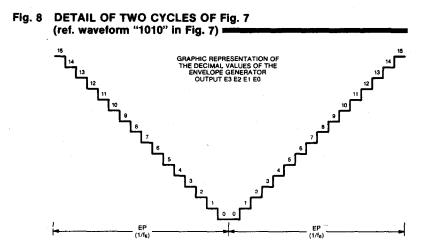

#### 3.5.2 ENVELOPE SHAPE/CYCLE CONTROL (Register R15)

The Envelope Generator further counts down the envelope frequency by 16, producing a 16-state per cycle envelope pattern as defined by its 4-bit counter output, E3 E2 EI E0. The particular shape and cycle pattern of any desired envelope is accomplished by controlling the count pattern (count up/count down) of the 4-bit counter and by defining a single-cycle or repeat-cycle pattern.

This envelope shape/cycle control is contained in the lower 4 bits (B3--B0) of register R15. Each of these 4 bits controls a function in the envelope generator, as illustrated in the following:

The definition of each function is as follows:

- Hold when set to logic "1", limits the envelope to one cycle, holding the last count of the envelope counter (E3--E0=0000 or 1111, depending on whether the envelope counter was in a count-down or count-up mode, respectively).

- Alternate when set to logic "1", the envelope counter reverses count direction (up-down) after each cycle.

NOTE: When both the Hold bit and the Alternate bit are ones, the envelope counter is reset to its initial count before holding.

To further describe the above functions could be accomplished by numerous charts of the binary count sequence of E3 E2 E1 E0 for each combination of Hold, Alternate, Attackand Continue. However, since these outputs are used (when selected by the Amplitude Control registers) to amplitude modulate the output of the Mixers, a better understanding of their effect can be accomplished via a graphic representation of their value for each condition selected, as illustrated in Figs. 7 and 8.

I/O Port Data Store

3.6 Registers R16 and R17 function as intermediate data storage registers between the PSG/CPU data bus (DA0--DA7) and the two I/O ports (IOA7-IOA0 and IOB7--10B0). Both ports are available in the AY-3-8910: only I/O Port A is available in the AY-3-8912. Using registers R16 and R17 for the transfer of I/O data has no effect at all on sound generation.

(Registers R16, R17)

To output data from the CPU bus to a peripheral device connected to I/O Port A would require only the following steps:

- 1. Latch address R7 (select Enable register)

- 2. Write data to PSG (setting B6 of R7 to "1")

- 3. Latch address R16 (select IOA register)

- 4. Write data to PSG (data to be output on I/O Port A)

To input data from I/O Port A to the CPU bus would require the following:

- 1. Latch address R7 (select Enable register)

- 2. Write data to PSG (setting B6 to R7 to "0")

- 3. Latch address R16 (select IOA register)

4. Read data from PSG (data from I/O Port A)

Note that once loaded with data in the output mode, the data will remain on the I/O port(s) until changed either by loading different data, by applying a reset (grounding the Reset pin), or by switching to the input mode.

Note also that when in the input mode, the contents of registers R16 and/or R17 will follow thesignals applied to the I/O port(s). However, transfer of this data to the CPU bus requires a "read" operation as described above.

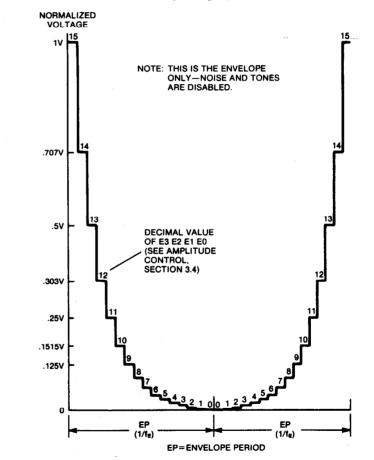

## D/A Converter Operation

3.7 Since the primary use of the PSG is to produce sound for the highly imperfect amplitude detection mechanism of the human ear, the D/A conversion is performed in logarithmic steps with a normalized voltage range of from 0 to 1 Volt. The specific amplitude control of each of the three D/A Converters isaccomplished by the three sets of 4-bit outputs of the Amplitude Control block, while the Mixeroutputs provide the base signal frequency (Noise and/or Tone).

Fig. 9 illustrates the D/A Converter output which would result if noise and tones were disabled and an envelope-controlled variable amplitude were selected.

#### Fig. 9 D/A CONVERTER OUTPUT (ref. Fig. 6)

## **4 INTERFACING**

# **4.1** Since the AY-3-8910/8912 PSG must be used with support components, interfacing to the circuit is an obvious requirement. The PSG is designed to be controlled by a microprocessor or microcomputer, and drive directly into analog audio circuitry. It provides the link between the computer and a speaker to provide sounds or sound effects derived from digital inputs.

The following paragraphs provide examples and illustrations showing the ease with which an AY-3-8910/8912 Programmable Sound Generator may be utilized in a microprocessor/microcomputer system.

## Clock Generation

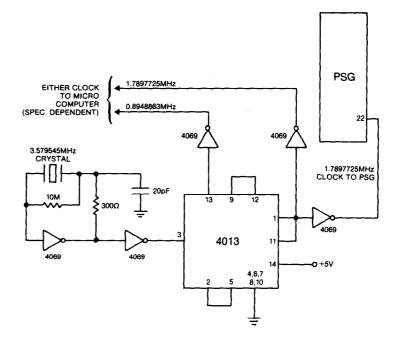

4.2 An economical solution to providing a system clock is shown in Fig. 15. It consists of a 3.579545MHz standard color burst crystal, a CD4089 CMOS inverter, and a CD4013 to divide the color burst frequency in half. The clock produced for the PSG runs at a 1.7897725MHz rate. Depending on the microcomputer used, its clock should be selected within its specified value.

## Fig. 15 CLOCK GENERATION

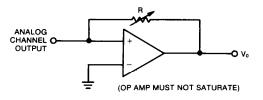

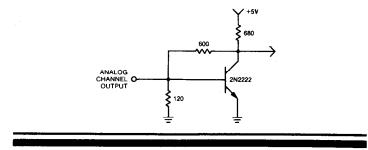

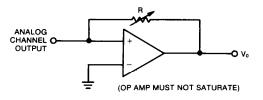

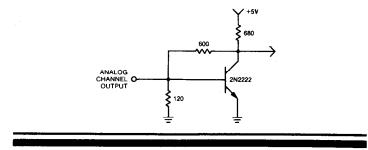

## 4.3 Audio Output Interface

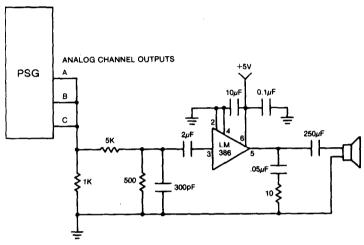

Fig. 16 illustrates the audio output connections to a commercially available LM386 audio amplifier. It shows channels A, B, and C summed together to enable complex waveforms to becomposed and amplified through a single external amplifier. These channels may be individually amplified through separate channels for more exotic sound systems.

Each output channel is individually controlled by separateamplitude registers (R10, R11, R12) and an enable register (R7) in the PSG.

## Fig. 16 AUDIO OUTPUT INTERFACE

External Memory Access

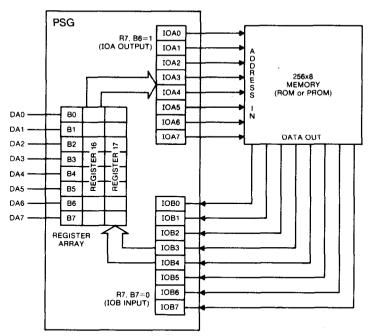

4 . 4 The ROM or PROM shown connected to the PSG in Fig. 17 illustrates an option for providing additional data information for processor support. The two I/O registers within the PSG are used in this case to address the memory via I/O Port A (8 Bits) and read data from the memory via I/O Port B (8 Bits).

An example of the bus control sequence to address and read an external memory connected to I/O ports A and B would be as follows (Assume Port A addresses and Port B reads):

|                                                                      | Bu   | IS COO | des |                                           |  |  |  |  |

|----------------------------------------------------------------------|------|--------|-----|-------------------------------------------|--|--|--|--|

| Bus Control                                                          | BDIR | BC2    | BC1 | Explanation of Bus Data (DA7DA0)          |  |  |  |  |

| Latch address                                                        | 1    | 1      | 1   | 00000111: Latch R7 to program I/O Ports   |  |  |  |  |

| Write to PSG                                                         | 1    | 1      | 0   | 01000000: Set B7. B6 to 0, 1 respectively |  |  |  |  |

| Latch address                                                        | 1    | 1      | 1   | 00001110: Latch R16 to address memory     |  |  |  |  |

| Write to PSG                                                         | 1    | 1      | 0   | 00000001: Address data to memory          |  |  |  |  |

| Latch address                                                        | 1    | 1      | 1   | 00001111: Latch R17 to read memory        |  |  |  |  |

| Read from PSG                                                        | 0    | 1      | 1   | XXXXXXXX: Memory data contained in R17    |  |  |  |  |

| NOTE: BC2 in the above Bus Codes may be permanently tied to +5V thus |      |        |     |                                           |  |  |  |  |

requiring only two bus control lines for all control operations (refer to Section 2.3 for a complete explanation).

Also, RAM or EAROM may be used in place of the ROM or PROM shown by altering the program to use PORT B as an I/O. Port B then will be able to write data as an output and read data as an input.

Fig. 17 EXTERNAL MEMORY ACCESS

1

## Microprocessor/ Microcomputer Interface

4.5 In Fig. 18, the lines identified DA7--DA0 are the input/output bus bits 7--0. This 8 bit bus is used to pass all data and address information between the AY-3-8910/8912 and the system processor.

BC1, BC2 and BDIR are bus control signals generated by the processor to direct all bus operations. These operations are identified as Latch Address, Write to PSG, Read from PSG, and Inactive.

The following Sections detail specific interfaces to several popular microprocessors/microcomputers.

Fig. 18 MICROPROCESSOR/MICROCOMPUTER INTERFACE

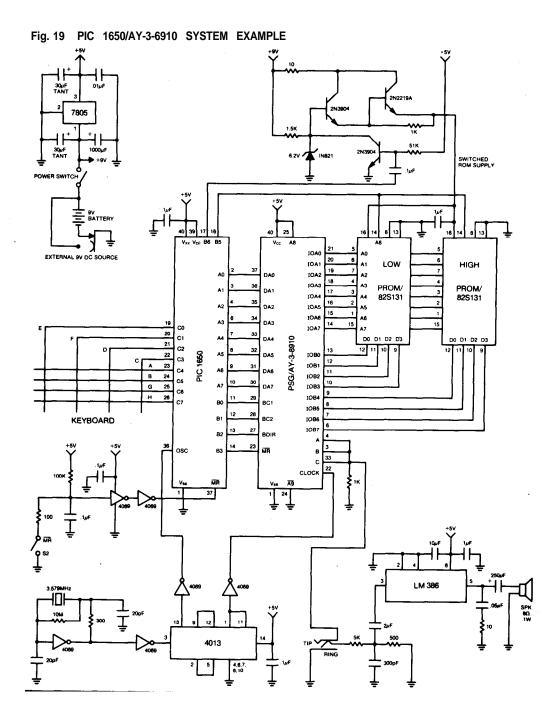

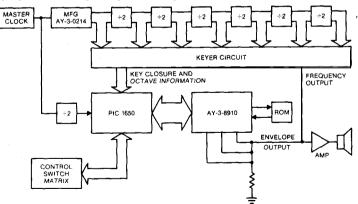

# Interfacing to the PIC 1650

4.6 Fig. 19 shows the schematic of an AY-3-8910 demonstrator circuit. This configuration uses a PIC 1650 as the main controller in the circuit. The PIC 1650 is used to scan the keyboard, fetch data from the PROMs, writedata to the AY-3-8910 and provide the timing for the AY-3-8910.

The interfacing is direct since the PIC 1650 and the AY-3-8910 operate with compatible supplies and input/output voltages.

This particular schematic illustrates how a microcomputer with additional memory can produce a stand-alone music and sound effects circuit. The circuit as shown operates with manual keyboard selections.

As Fig. 19 shows, the design for the interface connects directly to the output pins of the 1650 and the BC1, BC2, BDIR pins. The software then has the responsibility of manipulating these signals to signal the PSG to perform the proper address latch, read or write operations.

The program routine in this section illustrates code which is used in a hand-held demonstrator unit. This demonstration unit illustrates the range of PSG capabilities, including music, sound effects and I/O control. Note that the generalized routines perform the address latching before every read for convenience.

The "READ ROM" routine illustrates use of the generalized read and write routines to access the outside world through the PSG to read and write.

#### 4.6.1 WRITE DATA ROUTINE

| 80.<br>81.<br>82. |     |      | ADDR  | SS OF 8 | 50 TO 8910<br>910 REG IN '<br>E IN 'DATA' | ADDRES'                         |

|-------------------|-----|------|-------|---------|-------------------------------------------|---------------------------------|

|                   | 024 | 0066 | ,     | MOVWF   | ADDRES                                    |                                 |

|                   | 025 |      | WRITE | MOVE    |                                           | GET REGISTER NO.                |

|                   |     | 0045 |       | MOVWF   |                                           | SET ADDRESS                     |

|                   | 027 | 1006 |       |         | IOB.W                                     | GET PRESENT BC1, BC2, BDIR ETC. |

|                   |     | 7370 |       | ANDLW   |                                           | ,421111202111201,002,0011210.   |

|                   | 031 |      |       | IORLW   | 4                                         | :SET BAR                        |

|                   |     | 0046 |       | MOVWF   |                                           | SEND BAR                        |

|                   |     | 7370 |       | ANDLW   | 370                                       | ,oeito brut                     |

|                   |     | 0046 |       |         | IOB                                       | SEND NACT                       |

|                   |     | 1027 |       | MOVE    | DATA.W                                    |                                 |

|                   |     | 0045 |       | MOVWE   |                                           | PUT DATA ON D/A PINS OF 8910    |

| 94.               | 037 | 1006 |       | MOVE    | IOB.W                                     | ,                               |

| 95.               | 040 | 7370 |       | ANDLW   | 370                                       |                                 |

| 96.               | 041 | 6406 |       | IORLW   | 6                                         |                                 |

| 97.               | 042 | 0046 |       | MOVWF   | IOB                                       | SEND DWS                        |

| 98.               | 043 | 7370 |       | ANDLW   | 370                                       | SET UP NACT                     |

| <b>99</b> .       | 044 | 0046 |       | MOVWF   | IOB                                       | SEND NACT                       |

| 100.              | 045 | 4000 |       | RET     |                                           | RETURN TO CALLING ROUTINE       |

| 1 6             | 4.6.2 READ  | DATA ROUT                                        | INE         |                                 |  |  |  |  |

|-----------------|-------------|--------------------------------------------------|-------------|---------------------------------|--|--|--|--|

| 4.0             | 51.         | ADDRESS OF F                                     | READ IN REC | SISTER 'ADDRES'                 |  |  |  |  |

| Interfacing     | 52.         | AFTER READ, INPUT DATA IN REGISTER 'DATA'        |             |                                 |  |  |  |  |

|                 | 53.         | 3. ENTRANCE READ1 ASSUMES THAT REGISTER NUM IN W |             |                                 |  |  |  |  |

| to the PIC 1650 | 54.         | ;                                                |             |                                 |  |  |  |  |

|                 | 55.000 0066 | READ1 MOVWF                                      | ADDRES      | BYPASS ADDDRESS STORE           |  |  |  |  |

| (Cont)          | 56.001 1026 | READ MOVE                                        | ADDRES,W    | GET REGISTER NO.                |  |  |  |  |

| (Cont.)         | 57.002 0045 | MOVWF                                            | IOA         | ;MOVE TO 8910 D/A PINS          |  |  |  |  |

| <b>\ /</b>      | 58.003 1006 | MOVF                                             | IOB,W       | GET PRESENT BC1, BC2, BDIR ETC. |  |  |  |  |

|                 | 59.004 6404 | IORLW                                            | 4           | ;SET BAR                        |  |  |  |  |

|                 | 80 005 0046 |                                                  | IOR         | SEND BAD                        |  |  |  |  |

| 30. 003 | 1000 |       | 100,00 | , GET FREGERT BOT, DOZ, DDIT ETG |

|---------|------|-------|--------|----------------------------------|

| 59.004  | 6404 | IORLW | 4      | ;SET BAR                         |

| 60.005  | 0046 | MOVWF | IOB    | ;SEND BAR                        |

| 61.006  | 7370 | ANDLW | 370    |                                  |

| 62.007  | 0046 | MOVWF | IOB    | SEND NACT                        |

| 63.010  | 6377 | MOVLW | 377    |                                  |

| 64.011  | 0045 | MOVWF | IOA    | SET FOR INPUT                    |

| 65.012  | 1006 | MOVF  | IOB,W  |                                  |

| 66.013  | 7370 | ANDLW | 370    |                                  |

| 67.014  | 6403 | IORLW | 3      | ;SET DTB                         |

| 68.015  | 0046 | MOVWF | IOB    | SEND DTB                         |

| 69.016  | 1005 | MOVF  | IOA,W  |                                  |

| 70. 017 | 0067 | MOVWF | DATA   | SAVE DATA                        |

| 71.020  | 1006 | MOVF  | IOB,W  |                                  |

| 72. 021 | 7370 | ANDLW | 370    |                                  |

| 73. 022 | 0046 | MOVWF | IOB    | ;SEND NACT                       |

| 74. 023 | 4000 | RET   |        | RETURN TO CALLING ROUTINE        |

|         |      |       |        |                                  |

## 4.6.3 READ ROM ROUTINE

| 106.          |                            |           | ENTRANCE NEXROM           |  |  |

|---------------|----------------------------|-----------|---------------------------|--|--|

| 107.          | ADDRESS OF HO              | M IN HOMA | AD AT ENTRANCE ROMRD      |  |  |

| 108.          | ;                          |           |                           |  |  |

| 109.          | ;INCREMENTS RC             | MAD AFTE  | R READ, IF ROM ADDRESS    |  |  |

| 100.          | ;CROSSES 256 BC            | DRDER, MA | KE UPPER BANK SELECT = 1  |  |  |

| 111.          | ;                          |           |                           |  |  |

| 112.          | USES 8910 REG 1            | 6 FOR ADD | DRESS                     |  |  |

| 113.          | 8910 REG 17 FOR INPUT DATA |           |                           |  |  |

| 114.046 1030  | NEXROM MOVE                | ROMAD,V   | V                         |  |  |

| 115.047 0067  | ROMRD MOVWF                | DATA      | ;PUT ADDRESS              |  |  |

| 116.050 6016  | MOVLW                      | 16        | I/O A ADDRESS             |  |  |

| 117.051 0066  | MOVWF                      | ADDRES    |                           |  |  |

| 118.052 2306  | BCF                        | IOB,6     | TURN ON ROM               |  |  |

| 119. 053 4425 | CALL                       | WRITE     | SEND TO IOA               |  |  |

| 120. 054 1266 | INCF                       | ADDRES    | TO IOB ADDRESS            |  |  |

| 121.055 4401  | CALL                       | READ      | GET DATA                  |  |  |

| 122.056 2706  | BSF                        | IOB.6     | TURN OFF ROM              |  |  |

| 123. 057 1770 | INCFSZ                     | ROMAD     | TO NEXT LOC               |  |  |

| 124.060 4000  | RET                        |           |                           |  |  |

| 125.061 2646  | BSF                        | IOB,5     | SET HIGH SELECT           |  |  |

| 126. 062 4000 | RET                        |           | RETURN TO CALLING ROUTINE |  |  |

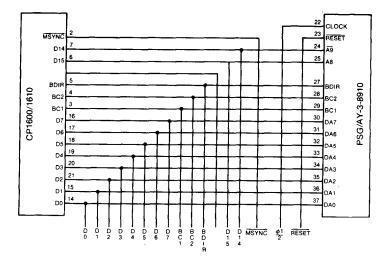

# Interfacing to the CP1600/1610

4.7 As shown in Fig. 20, the wiring is direct between the AY-3-8910 and a CP1600/1610 microprocessor. The levels are compatible thus eliminating any need for level converters. Even the terminology between the IC's remains constant to provide simple-to-follow connections.

The CP1600/1610 acts as a controller in this configuration fetching data from ROM's contained elsewhere in the system. The CP1600/ 1610 also acts as the bus controller developing the necessary timing for the AY-3-8910.

4.7.1 WRITE DATA ROUTINE

The program necessary to write to a selected register is as follows: MVI value, R0; move in value to be written MVO R0, Reg; write to register

The routine to load all registers with the same value is as follows: MVII Reg 0, R4 CLRR R0 Here MVO@ RO, R4

CMPI Reg 0 + 17, R4 BLT Here

4.7.2 READ DATA ROUTINE

The routine to read from a selected register is as follows: MVI Reg, RO; get data from reg in R0 MVO R0, value; store in memory

Fig. 20 CP1600/1610/AY-3-8910 INTERFACE

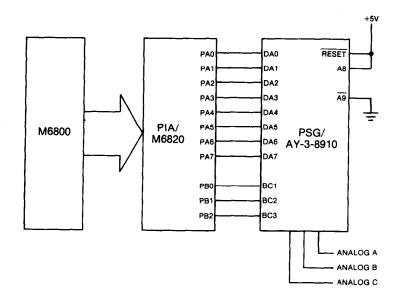

## Interfacing to the M6800

4.8 An M6800 microprocessor can be interfaced with an AY-3-8910/8912 through the addition of an M6820 PIA chip. The I/O portsdesignated as PA0 to PA7 are used as the 8 bit bus lines and I/O ports PB0 to PB2 are used as the bus control lines. The software routines shown are used to control the latch address, write data, and read data functions for the AY-3-8910/8912.

4.8.1 LATCH ADDRESS ROUTINE ;AT ENTRY, B HAS ADDRESS VALUE

LATCH CLRA STAA 8005 ;GET D DIR A LDAA #FF STAA 8004 ;OUTPUTS LDAA #4 STAA 8005 ;GET PERIPHERAL A STAB 8004 ;FORM ADDR STAA 8006 CLRA STAA 8006 ;LATCH ADDRESS RTS ;RETURN

4.8.2 WRITE DATA ROUTINE ;AT ENTRY, B HAD DATA VALUE

WRITE STAB 8004 ;FORM DATA LDAA #6 ;DWS STAA 8006 CLRA STAA 8006 ;WRITE DATA RTS ;RETURN

I

4.8.3 READ DATA ROUTINE ;AFTER READ, B HAS READ DATA

READ STA A 8005 ;GET D DIR STA A 8004 ;INPUTS LDAA #4 STA A 8005 ;GET PERIPHERAL DECA STA A 8006 ;READ MODE LDA B 8004 ;READ DATA CLRA STA A 8006 ;REMOVE READ MODE RTS ;RETURN

## Fig. 21 M6800/AY-3-8910 INTERFACE

# 4.9 to the 8080 S100 Bus

The sample S100 bus design provides for reading and writing the PSG using only an 8080 "IN" or "OUT" instruction to the proper Interfacing address. Another feature of the design is the provision for multiple PSG devices to be connected to a single bus. The system described is presently running two PSG's, one to each of two stereo channels.

> As can be seen from the read and write routines in the illustrative program, the program overhead necessary to communicate with the PSG is minimal.

4.9.1 LATCH ADDRESS ROUTINE

PORTADDR EQU 80H ;ADDRESS TRANSFER PORT ADDRESS PORTDATA EQU 81H :DATA TRANSFER PORT ADDRESS

THIS ROUTINE WILL TRANSFER THE CONTENTS OF ;8080 REGISTER C TO THE PSG ADDRESS REGISTER MOV A,C ;GET C IN A FOR OUT PSGBAR

OUT PORTBAR ;SEND TO ADDRESS PORT RET

4.9.2 WRITE DATA ROUTINE

ROUTINETO WRITE THE CONTENTS OF 8080 REGISTER B ;TO THE PSG REGISTER SPECIFIED BY 8080 REGISTER C

PSGWRITE CALL PSGBAR :GET ADDRESS LATCHED MOV A.B, ;GET VALUE IN A FOR TRANSFER RET PORTDATA ;PUT TO PSG REGISTER

4.9.3 READ DATA ROUTINE

ROUTINE TO READ THE PSG REGISTER SPECIFIED ;BY THE 8080 REGISTER C AND RETURN THE DATA :IN 8080 REGISTER B

PSGREAD CALL PSGBAR

| IN  | PORTDATA ;GET REGISTER DATA  |

|-----|------------------------------|

| MOV | B,A GET IN TRANSFER REGISTER |

| RET |                              |

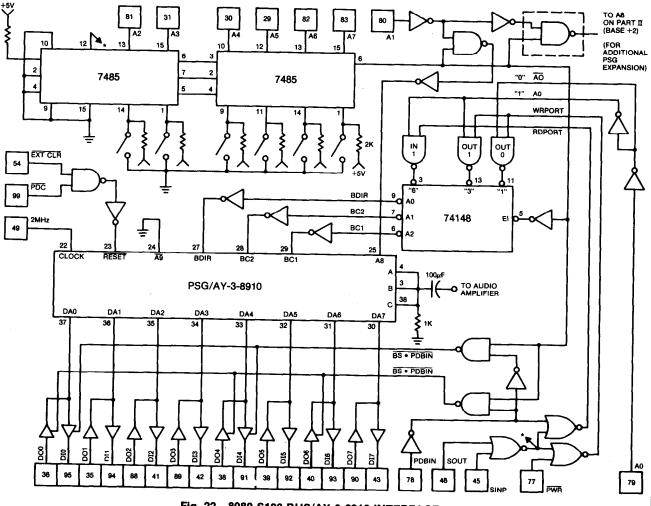

Fig. 22 8080 S100 BUS/AY-3-8910 INTERFACE

# **5 MUSIC GENERATION**

The production of music involves the creation of series of frequencies which are pleasing to the human ear (setting critical evaluation aside). This involves essentially mathematical relationships, making the application ideal for digital devices. For example, the shifting up or down in octaves is a multiplication or division by a power of 2, which is a simple shift operation for most microprocessors.

Another factor in music generation is "communication". The composer must be able to convey his tune ideas so that a musician or group of musicians can reproduce the composer's ideas-often on widely differing instruments. This concept involves "tuning" the instruments to a standard set of frequencies and following a set rhythm pattern. The tuning frequency most widely used is based on the third octave note "A" of 440Hz, the "Equal Tempered Chromatic Scale".

Although it is easy to construct recognizable tunes using only one note at a time, the simultaneous sounding of more than one note to produce chords and counterpoint vastly increases the quality of the sound. This feature is easily achieved in the PSG since three channels are provided, each independently programmable.

5.1 Since notes are formed by sustaining a particular frequency for a preset period of time at a varying amplitude, the PSG performs this function with a series of simple register loads. The method used in many cases is to obtain register load values for first octave notes and to shift to the correct octave at playtime.

> The chart in Fig. 23 lists a full 8 octaves of notes from a low of CI (32.703Hz) to a high of B8 (7902.080Hz). Assuming an input clock frequency of 1.78977MHz (one half the standard "color" crystal frequency of 3579545MHz), and applying the formulas of Section 3.1 for calculating Tone Period register load values, results in the register values shown. The nature of the PSG divider scheme produces a high degree of accuracy for low frequencies, less for high frequencies. This can be seen in the chart in the comparison of "ideal frequencies" and "actual frequencies", with the ideal frequencies being those of the Equal Tempered Chromatic Scale, and the actual frequencies being the "best fit" values from the formula calculation.

Note Generation

| 12-BIT REGISTER<br>VALUE IN OCTAL | 6       | 2        | 6       | 4        | 2       | c       | ~       |         |         | . ~     | . 0            | -       | e               | S          | ~        | 2          | S        | •          | 4                | ~ (        |          | > -      | •        | ŝ            | 2           | 0        | s c                   | NC            | o co       | 4                  | 0          | <b>D</b> ( | •          | 10       | -        | •        | 9          | ŝ        | 4 0           | ° °          | ч <del>г</del> | - 0      | -                  |

|-----------------------------------|---------|----------|---------|----------|---------|---------|---------|---------|---------|---------|----------------|---------|-----------------|------------|----------|------------|----------|------------|------------------|------------|----------|----------|----------|--------------|-------------|----------|-----------------------|---------------|------------|--------------------|------------|------------|------------|----------|----------|----------|------------|----------|---------------|--------------|----------------|----------|--------------------|

| N OF                              | 2       | -        | 2       | 9        | ŝ       | 4       | •       | -       | ·c      | ~       | ~              | 9       | ŝ               | 4          | e        | ო          | 2        | 2          | -                | 0 0        | 00       | <b>~</b> |          | 9            | 9           | 9        | ŝ                     | n u           | 4          | 4                  | 4.         | 4 0        | <b>.</b> . | <b>ი</b> | e        | e        | 2          | ~ ~      | NC            | vc           | 10             | 101      | -                  |

|                                   | 3       | ო        | 2       | 2        | 2       | 5       | 10      | 10      | 10      | •       | -              | -       | -               | -          | -        | -          | -        | -          | -                | - 1        | ~ •      | - c      | 。<br>。   | 0            | 0           | 0        | 0 0                   | <b>&gt;</b> < | 0          | 0                  | 0          | 2 0        | > c        | 0        | 0        | 0        | 0          | 0        | <b>&gt;</b> 0 | - c          | 。<br>c         | 0        | 0                  |

| 12-8<br>VAL                       | 0       | 0        | 0       | 0        | 0       | c       |         | , c     | • c     | 0       | 0              | 0       | 0               | 0          | 0        | 0          | 0        | 0          | 0                | 0 0        | - c      | > c      | , o      | 0            | 0           | 0        | 0 0                   | - c           | , o        | 0                  | 0          | - c        | - c        | 0        | 0        | 0        | 0          | 0 0      | - c           |              | , c            | 0        | 0                  |

| ACTUAL<br>FREQUENCY               | 522.714 | 553.766  | 588.741 | 621.449  | 658.005 | 699.130 | 740,800 | 782 243 | 828.598 | 880.794 | 932.173        | 989.918 | 1045.428        | 1107.532   | 1177.482 | 1242.898   | 1316.009 | 1398.260   | 1471.852         | 15/5.504   | 1747 825 | 1864 346 | 1962.470 | 2110.581     | 2237.216    | 2330.433 | 2485.795<br>Deeg of o | 2706 520      | 2943.705   | 3107.244           | 3290.023   | 3728 603   | 3995 028   | 4142.992 | 4474.431 | 4660.866 | 5084.581   | 5326.704 | 0083.039      | 6214 488     | 6580.046       | 6991.299 | 7457.385           |

| IDEAL<br>FREQUENCY                | 523.248 | 554.368  | 587.328 | 622.256  | 659.248 | 698.464 | 739.984 | 783.984 | 830.608 | 880.000 | 932.320        | 987.760 | 1046.496        | 1108.736   | 1174.656 | 1244.512   | 1318.496 | 1396.928   | 1479.968         | 506./0CI   | 1760 000 | 1R64 640 | 1975.520 | 2092.992     | 2217.472    | 2349.312 | 2489.024<br>2626 002  | 2793 856      | 2959.936   | 3135.936           | 3322.432   | 3729.280   | 3951.040   | 4185.984 | 4434.944 | 4698.624 | 4978.048   | 52/3.964 | 211.1000      | 6271 872     | 6644.864       | 7040.000 | 7458.560           |

| OCTAVE                            | 9       | 2        | ŝ       | Ŋ        | S       | S       | ŝ       | 20      | ŝ       | ŝ       | 5              | 5       | 9               | 9          | g        | 9          | 9        | 6          | 00               | 0 4        | o "      |          | 9        | 7            | ~           | ~ •      |                       | - 1-          | 7          | ~                  | ~ ~        |            |            | 80       | 80       | œ (      | 20 0       | 00       | 0 0           | ) ac         | 0              | 80       | æ (                |

| NOTE                              | o       | <b>*</b> | ۵       | <b>#</b> | ш       | u.      | #<br>   | σ       | #0      | •       | ¥¥             | 8       | o               | <b>*</b>   | ٥        | <b>*</b>   | ш        | Ľ          | <b>ٿ</b> ر       | 5 đ        | 5⊲       | **       | 60       | ပ            | ₿,          | 02       | 5 u                   | J 144         | ŧ.         | g                  | <u>*</u> < | (₹         | B          | o        | ð        | ם מ      | <b>5</b> u | 11       | . 4           |              | 10             | ×        | <b>*</b> ∢(        |

| ar<br>Ar                          | 5       | 4        | 2       | 4        | e       | 0       | e       | e       | e       | ~       | 0              | 4       | 9               | 9          | 4        | (C)        | ç,       | -,         | - u              | ה ינ       | o ←      | 0        | 2        | 7            | ~ `         | 2        |                       | - +           | 2          | <b>с</b> о         |            | r 0        | 5          | 4        | 4        | ŝ        | 5,0        | <i>.</i> | ¢<br>م        | 2            | Q.             | 9        | 00                 |

| 12-BIT REGISTER<br>/ALUE IN OCTAL | ო       | 3        | 4       | ~        | ო       | 0       | 9       | ŝ       | \$      | 9       | 0              | 2       | ŝ               | -          | ç        | <b>с</b> , | - (      | <b>)</b> r | - 4              | <b>.</b> . | ~        | 0        | -        | 2            | 41          | ~ •      | - 4                   | • 0           | ო          | ~ (                | <b>n</b> r | . 4        | 0          | ŝ        | 2        | ~ 4      | n r        | ۷ C      | o vo          | <b>ا</b> ر ا | -              | 2        | œ٦                 |

|                                   | ŝ       | ŝ        | ~       | 4        | 2       | 0       | ŝ       | ო       | -       | ~       | 9              | 4       | ~               | -          | ~        | 9          | ۰ n      | 4 (        | N <del>-</del>   | - c        | ~        | ~        | 9        | ŝ            | 4 (         |          | ° 0                   | 10            | -          | 0                  | 2 1        | . ~        | 2          | 9        | 9        | م        | n u        | n u      | , <b>च</b>    | 4            | 4              | e        | <i>.</i>           |

| 12-BIJ<br>VALUI                   | g       | 9        | ŝ       | ŝ        | ŝ       | ŝ       | 4       | 4       | 4       | ო       | 3              | e l     | <del>ເ</del> ບັ | <b>m</b> ( | 2        | ~ ~        | N        | NC         | ~ ~              | • •        | ı        | -        | -        | -            | - •         |          |                       | ·             | -          | - •                | - 0        | 0          | 0          | 0        | 0        |          | - c        | > c      | 。<br>。        | 0            | 0              | 0        | 00                 |

| ACTUAL<br>FREQUENCY               | 32.698  | 34.653   | 36.712  | 38.895   | 41.201  | 43.662  | 46.243  | 48.997  | 51.908  | 54.995  | 58.261         | 61.733  | 65.416          | 69.307     | 73.399   | 00,100     | 62.432   | 01.323     | 92.320<br>08 037 | 103.863    | 109.991  | 116.522  | 123.467  | 130.831      | 138.613     | 155 578  | 164.743               | 174.510       | 184.894    | 195.903            | 201.004    | 233.043    | 246.933    | 261.357  | 276.883  | 240.756  | 320 073    | 349 565  | 370.400       | 392.494      | 415.839        | 440.397  | 466.087            |

| IDEAL<br>FREQUENCY                | 32.703  | 84.948   | 36.708  | 38.891   | 41.203  | 43.654  | 46.249  | 48.999  | 51.913  | 55.000  | 58.270         | 61.735  | 65.406          | 69.296     | 73.416   | 11./82     | 07.200   | 005.100    | 92.430           | 103.826    | 110.000  | 116.540  | 123.470  | 130.812      | 138.592     | 155 564  | 164.812               | 174.616       | 184.996    | 195.996<br>207 een | 220.000    | 233.080    | 246.940    | 261.624  | 2//.184  | 211 128  | 329 624    | 349.232  | 369.992       | 391.992      | 415.304        | 440.000  | 466.160<br>403 peo |

| OCTAVE                            |         |          | - ,     |          |         | -       | -       | -       | -       | -       | <del>.</del> . | - (     | N               | N          | 2 1      | NC         | 40       | 10         | 10               | 101        | 2        | ~        | 0        | <b>с</b> о с | ,<br>,<br>, | 00       |                       | 3             | <b>с</b> ( |                    | <b>,</b> თ | <b>n</b>   | ю.         | 4.       | 4 4      | 4 4      | r •9       | 4        | 4             | 4            | 4              | 4,       | 4 4                |

| •                                 |         |          |         |          |         |         |         |         |         |         |                |         |                 |            |          |            |          |            |                  |            |          |          |          |              |             |          |                       |               |            |                    |            |            |            |          |          |          |            |          |               |              |                |          |                    |

## 5.2 Tune Entry/ Playback

One of the methods of entering a composition into a computer memory would be to utilize a keyboard to pass number and alphabetic information concerning the composer's wishes. An alternate method would be to scan a positional series of switches (like a piano keyboard) to determine note, volume and duration data.

Since flexibility in tune entry is desired, it is important to allow the composer to specify certain constants of entry such as octave, pitch or tempo, and have these entries normalized to a known value.

## 5 3 Tune Variations

One of the significant features of a microcomputer based music player is the ability to modify the tune once it has been recorded. Among the simpler variations are:

#### 5.3.1 OCTAVE SHIFT

If an octave constant is added to the octave of the recorded note prior to storing the value in the PSG register, dynamic pitch changes can be obtained. The programming effect would be to shift one bit left for each lower octave and one bit right for each higher octave. For example, the effect will be that a tune written to play on a piano will sound like bells if a multiple octave up modification is performed.

#### 5.3.2 KEY

One measure of the virtuosity of a musician is his ability to modify the "key" or suboctave shift of a composition. The logical description of key transposition is to shift each note up or down by a predetermined number of notes from the original. For example, a piece written in C and played in C# would have all C notesshifted to C#, C# shifted to D, etc. (Note that the case must be considered where B of one octave is shifted to C of the next higher octave.) All of theseoperations require that the one of twelve note identification must be retained in the recorded representation.

## 5.3.3 TEMPO

The duration of each recorded note is best expressed in terms of "ticks" of an overall "tempo clock". At playtime, the total duration can be obtained by programatically multiplying the individual note to "slow down" or "speed up" the tune without changing the crucial time relationship between the notes. This can be accomplished by imbedding the note timing loops within the tempo timing loops for simple operation.

#### 5.3.4 CHORDS

There are-certain combinations of notes which when played simultaneously produce pleasant combinations. These "chords" can be easily formed from a base note by performing octave and key changes on two notes, which are played with the main note. These relationships are illustrated in Fig. 24, which lists the various note constants which will produce musical chords. A chord with a particular quality may be formed by playing its root, a 3rd Minor or Major, and other notes from the chord chart. For example, a C Major chord is formed from C(/2), E(/2), and G(/2).

Fig. 24 CHORD SELECTION CHART

| Chord<br>Selection                     | Root                                                                                                                                                                                                                                        | 3rd Minor                                                                                                                                                                                                                                                                                                                                                                                    | 3rd Major                                                                                                                                    | 4th                                                                                                                                                                                                                                                                                 | 5th                                                                                                                                                                                              | 6th                                                                                                           | 7th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |